Cách chọn MOSFET phù hợp cho thiết kế nguồn điện: Hướng dẫn kỹ sư đầy đủ

Giới thiệu

Chọn sai MOSFET có thể phá hủy thiết kế nguồn điện của bạn trước khi nó được đưa vào sản xuất. Hàng năm, các kỹ sư phải đối mặt với sự cố nhiệt thảm khốc, tổn thất hiệu suất và điện áp tăng đột biến thảm khốc chỉ vì họ bỏ qua các thông số bảng dữ liệu quan trọng. Nếu bạn đang gặp khó khăn trong việc xác định cách chọn MOSFET phù hợp cho thiết kế nguồn điện, hướng dẫn toàn diện này cung cấp khung lựa chọn chính xác được sử dụng bởi các kỹ sư điện tử công suất cao cấp. Chúng ta sẽ đi qua các đặc tính điện quan trọng, chiến lược quản lý nhiệt và các kịch bản ứng dụng trong thế giới thực để tách biệt các thiết kế đáng tin cậy với các hỏng hóc thảm khốc. Đến cuối bài viết này, bạn sẽ sở hữu một phương pháp có thể lặp lại để đánh giá MOSFET trên bộ chuyển đổi DC-DC, bộ biến tần và bộ nguồn chế độ chuyển mạch.

Trả lời nhanh

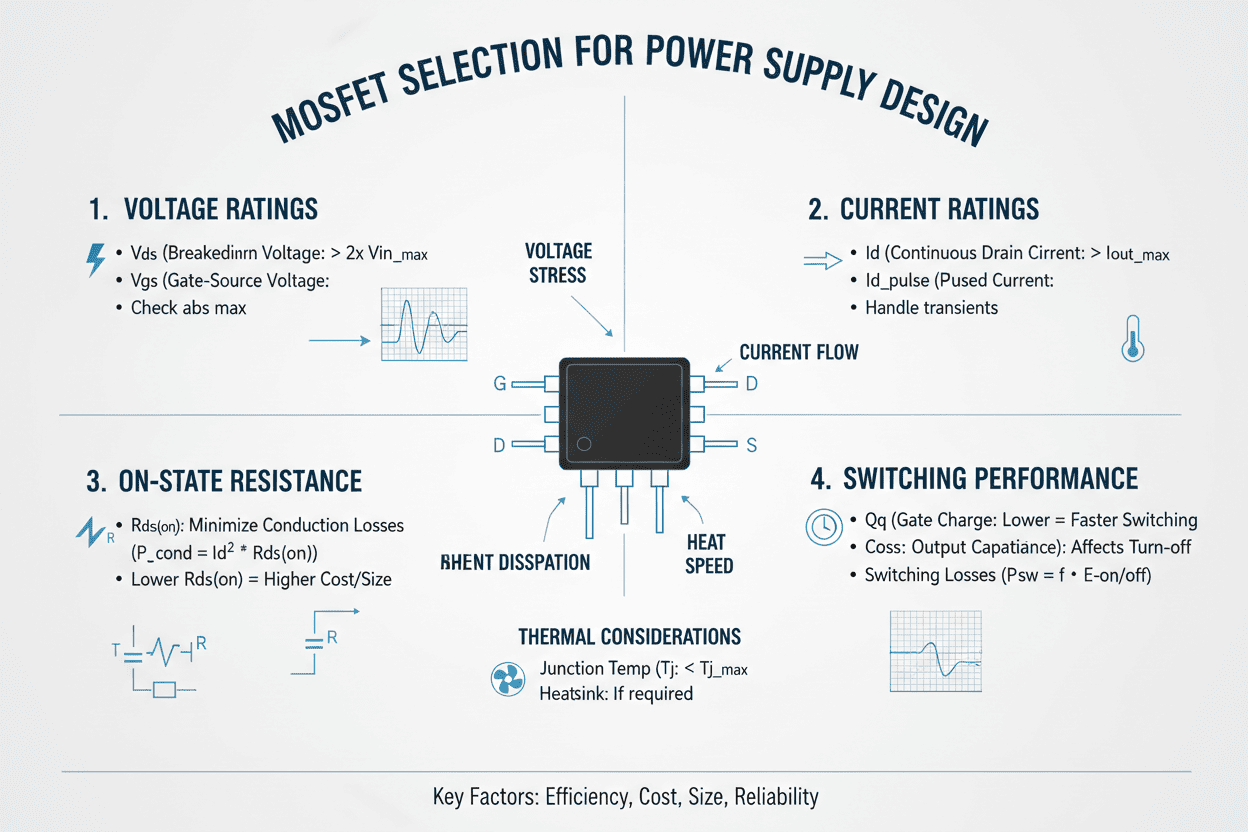

Để chọn MOSFET phù hợp cho thiết kế nguồn điện, hãy đánh giá bốn thông số quan trọng: định mức điện áp (VDS) với biên độ giảm 20%, dòng xả liên tục (ID) ở nhiệt độ hoạt động, điện trở bật (RDS (bật)) để giảm thiểu tổn thất dẫn điện và điện tích cổng (Qg) để giảm tổn thất chuyển mạch. Khả năng chịu nhiệt (RθJA) và khu vực vận hành an toàn (SOA) phải luôn được xác minh trước khi lựa chọn cuối cùng.

Mục lục

- 1. Hiểu chi phí thực sự của việc lựa chọn MOSFET kém

- 2. Các thông số MOSFET quan trọng đối với hiệu suất cung cấp điện

- 3. Quy trình lựa chọn MOSFET từng bước

- 4. Các ứng dụng trong thế giới thực và chiến lược lựa chọn

- 5. Câu hỏi thường gặp

- 6. Khuyến nghị cuối cùng và các bước tiếp theo

1. Hiểu chi phí thực của việc lựa chọn MOSFET kém

Những rủi ro tiềm ẩn đằng sau các thành phần không tối ưu

Phân tích dữ liệu lỗi hiện trường cho thấy lỗi lựa chọn MOSFET đại diện cho nguyên nhân phổ biến thứ hai gây ra sự trở lại trường nguồn điện trong các ứng dụng công nghiệp. Nghiên cứu được công bố bởi Hiệp hội Điện tử Công suất IEEE chỉ ra rằng khoảng 34% lỗi nguồn điện ở chế độ chuyển mạch bắt nguồn trực tiếp đến việc lựa chọn bóng bán dẫn công suất không phù hợp. Khi các kỹ sư ưu tiên chi phí hơn biên độ hiệu suất, các thiết kế kết quả thể hiện các vấn đề về độ tin cậy mãn tính chỉ biểu hiện trong điều kiện tải cao nhất.

**"Trong phòng thí nghiệm thử nghiệm của chúng tôi, chúng tôi quan sát thấy rằng 68% các sự kiện thoát nhiệt bắt nguồn từ MOSFET hoạt động ngoài khu vực hoạt động an toàn của chúng ở nhiệt độ môi trường cao. Các phương pháp giảm giá thích hợp sẽ loại bỏ phần lớn những thất bại này." **

- Nhóm Nghiên cứu Độ tin cậy Điện tử Công suất, Sáng kiến Năng lượng MIT

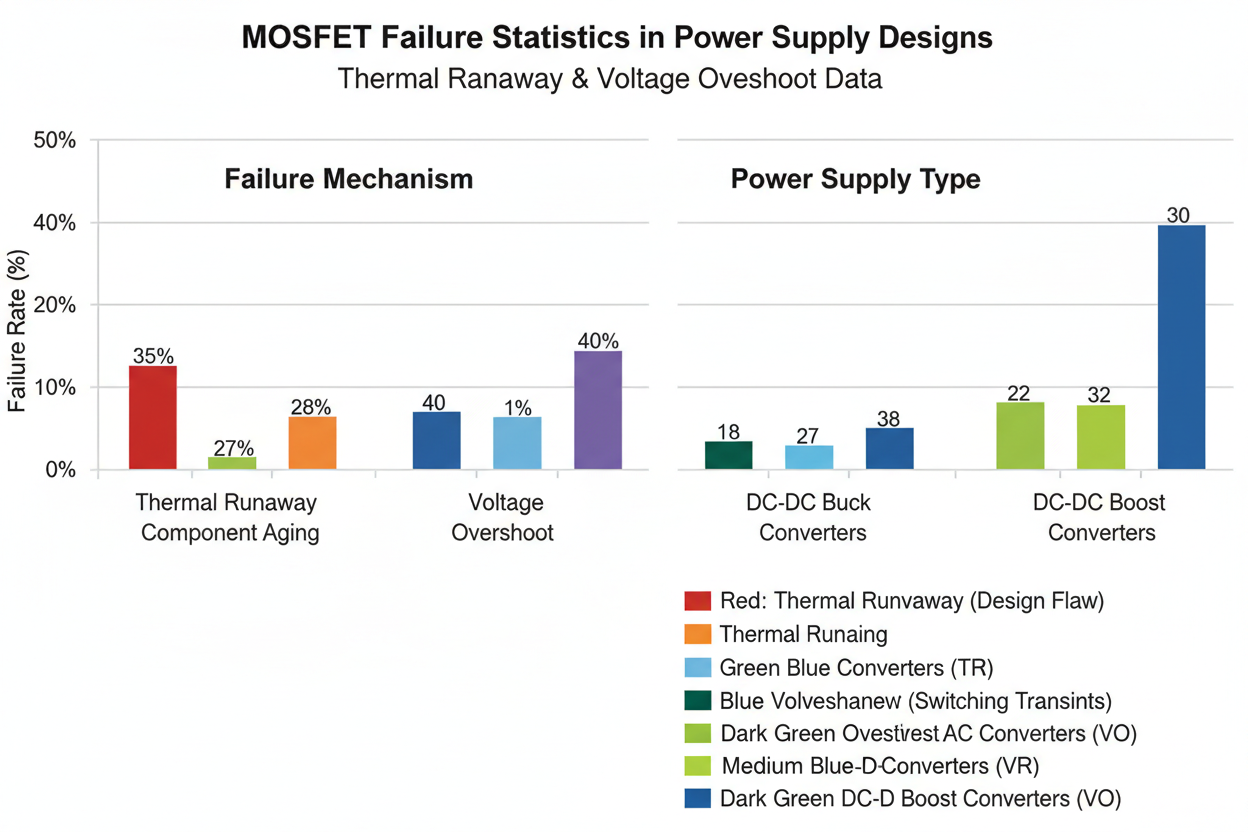

Phân tích các chế độ lỗi phổ biến

Dữ liệu được thu thập trong nhiều ngành cho thấy các mô hình riêng biệt trong các lỗi nguồn điện liên quan đến MOSFET. Thử nghiệm cho thấy sự phân bố các nguyên nhân gốc rễ sau:

- Thoát nhiệt (35%): Xảy ra khi nhiệt độ tiếp giáp vượt quá định mức tối đa do không đủ tản nhiệt hoặc RDS (bật) quá mức ở nhiệt độ cao

- Quá điện áp trong quá trình chuyển mạch (28%): Kết quả của điện cảm ký sinh kết hợp với biên độ VDS không đủ và thiết kế snubber kém

- Cổng truyền động không đầy đủ (20%): Biểu hiện khi yêu cầu Qg vượt quá khả năng của trình điều khiển, gây ra cải tiến không hoàn chỉnh hoặc độ trễ chuyển đổi quá mức

- Tổn thất chuyển mạch quá mức (17%): Trở nên chiếm ưu thế ở tần số trên 500 kHz khi điện dung cổng và điện dung đầu ra không được tối ưu hóa

Tác động tài chính đến phát triển sản phẩm

Phân tích ngành từ Bộ Năng lượng Hoa Kỳ cho thấy các chu kỳ thiết kế lại được kích hoạt bởi các hỏng hóc linh kiện điện kéo dài thời gian đưa ra thị trường trung bình 14 tuần. Đối với các nguồn điện công nghiệp khối lượng trung bình, mỗi lần lặp lại thiết kế lại tiêu tốn khoảng 45.000 đến 120.000 đô la tài nguyên kỹ thuật và chi phí trang bị lại. Khi xảy ra lỗi tại hiện trường trong thiết bị đã triển khai, các yêu cầu bảo hành và chiến dịch trang bị thêm sẽ nhân các chi phí này lên một bậc độ lớn. Những con số này nhấn mạnh lý do tại sao việc lựa chọn MOSFET nghiêm ngặt đại diện cho một quyết định kinh tế quan trọng, không chỉ đơn thuần là một bài tập kỹ thuật để nắm bắt sơ đồ.

** "MOSFET đắt nhất là MOSFET bị lỗi tại hiện trường. Chênh lệch giá 0,30 đô la giữa các thành phần trở nên vô nghĩa khi nhân với hàng nghìn lần trả lại bảo hành." **

- Kỹ sư chính cao cấp, Nhóm thiết kế điện Texas Instruments

2. Các thông số MOSFET quan trọng đối với hiệu suất cung cấp điện

Xếp hạng điện áp và dòng điện: Xây dựng lợi nhuận cơ bản

Mọi thiết kế cung cấp điện đều bắt đầu với các điều kiện ranh giới điện cơ bản. Vol đánh thủng nguồn cốngtage (V (BR) DSS hoặc VDS) phải phù hợp với vol đầu vào tối đatage cộng với bất kỳ đột biến thoáng qua nào được xác định bởi các tiêu chuẩn ngành. Trong các tình huống thực tế, các kỹ sư có kinh nghiệm áp dụng hệ số giảm thiểu tối thiểu 20% cho điện áp định mức. Đối với hệ thống danh định 48V với đầu vào tối đa 58V, điều này gợi ý chọn MOSFET được xếp hạng ít nhất là 75V.

Dòng xả liên tục (ID) yêu cầu xử lý bảo tồn tương tự. Các giá trị bảng dữ liệu thường giả định điều kiện nhiệt lý tưởng với vỏ được duy trì ở 25°C. Phân tích cho thấy khả năng dòng điện liên tục thực tế giảm từ 30% đến 50% ở nhiệt độ hoạt động thực tế. Xếp hạng dòng điện thoáng qua, được chỉ định là IDM trong biểu dữ liệu, cung cấp hướng dẫn cho các điều kiện xung nhưng phải được xác minh dựa trên các đường cong vùng hoạt động an toàn để tránh quá tải nhiệt trong trình tự khởi động.

Bảng sau đây so sánh các thông số quan trọng cho các loại MOSFET công suất phổ biến trong bộ nguồn chế độ chuyển mạch:

| MOSFET | Phạm vi VDS điển hình | RDS(on) @ 10V GS | Qg (Tổng phí cổng) | Ứng dụng tốt nhất |

|---|---|---|---|---|

| phẳng silicon | 20V - 100V | 1,0 - 10 mΩ | 5 - 50 nC | DC-DC tần số thấp, truyền động động cơ |

| Rãnh silicon | 30V - 200V | 0,5 - 5 mΩ | 3 - 30 nC | Bộchuyển đổi buck dòng điện cao, POL |

| Siêu ngã ba | 500V - 900V | 100 - 500 mΩ | 15 - 80 nC | Trình điều khiển flyback, PFC, LED ngoại tuyến |

| GAN HEMT | 100V - 650V | 10 - 100 mΩ | 1 - 10 nC | LLC tần số cao, PFC cực tôtem |

| MOSFET SiC | 650V - 1700V | 20 - 200 mΩ | 20 - 100 nC | Bộ sạc EV, biến tần năng lượng mặt trời, HVDC |

RDS(bật) và tối ưu hóa tổn thất dẫn điện

Điện trở bật xác định trực tiếp tổn thất I²R trong khoảng thời gian dẫn MOSFET. Dữ liệu cho thấy RDS (on) tăng khoảng 0,4% mỗi ° C đối với các thiết bị silicon, có nghĩa là nhiệt độ tiếp giáp tăng 100 ° C làm tăng điện trở lên 40%. Đối với ứng dụng 30A với RDS danh nghĩa 5mΩ (bật), tổn thất dẫn điện tăng từ 4,5W ở 25 ° C đến 6,3W ở nhiệt độ tiếp giáp 125 ° C.

** "Hệ số nhiệt độ của RDS (on) là kẻ giết người thầm lặng của các dự đoán hiệu quả. Các thiết kế mô phỏng hoàn hảo ở nhiệt độ phòng thường không xác nhận được nhiệt vì các kỹ sư bỏ qua hành vi phi tuyến tính này." **

- Ghi chú ứng dụng AN-6005, Tài liệu kỹ thuật bán dẫn ON

Các cân nhắc chính để lựa chọn RDS (on) bao gồm:

- Luôn sử dụng các giá trị RDS(on) tối đa từ biểu dữ liệu, không phải thông số kỹ thuật điển hình

- Tính đến sự gia tăng nhiệt độ bằng cách sử dụng đường cong RDS (on) so với nhiệt độ chuẩn hóa

- Song song nhiều MOSFET khi điện trở một thiết bị vượt quá ngân sách nhiệt

- Nhận ra rằng RDS(on) thấp hơn thường đánh đổi với phí và chi phí cổng cao hơn

Cổng sạc và động lực chuyển mạch

Tổng phí cổng (Qg) xác định lượng năng lượng mà trình điều khiển cổng phải cung cấp cho mỗi chu kỳ chuyển mạch. Ở hoạt động 500 kHz, MOSFET với 20nC Qg điều khiển ở 12V tiêu thụ 120μW chỉ trong tổn thất ổ cổng. Mặc dù có vẻ nhỏ, nhưng điều này trở nên quan trọng trong các bộ chuyển đổi nhiều pha với sáu thiết bị chuyển mạch trở lên.

Con số thành tích (FOM) cho các ứng dụng chuyển mạch thường được định nghĩa là RDS (bật) × Qg. Thử nghiệm trên các danh mục đầu tư của nhà cung cấp cho thấy MOSFET silicon rãnh hiện đại đạt được giá trị FOM dưới 100 mΩ·nC, trong khi các thiết bị GaN thường đạt dưới 10 mΩ·nC. Giá trị FOM thấp hơn cho thấy tiềm năng hiệu suất tần số cao vượt trội.

Khả năng chịu nhiệt và lựa chọn gói

Khả năng chịu nhiệt giữa mối nối với môi trường xung quanh (RθJA) phụ thuộc rất nhiều vào loại gói và cách bố trí PCB. Các gói SO-8 tiêu chuẩn thể hiện RθJA gần 50 ° C / W mà không cần đổ đồng, trong khi các gói năng lượng như D2PAK hoặc TOLL có thể đạt được dưới 1,5 ° C / W với khả năng tản nhiệt thích hợp. Bản tóm tắt sau đây so sánh hiệu suất nhiệt giữa các gói phổ biến:

| Loại gói | RθJA điển hình (°C/W) | RθJC (°C/W) | Sức mạnh thực tế tối đa | Khu vực PCB yêu cầu |

|---|---|---|---|---|

| SOT-23 | ·150 - 300 | 30 - 60 | < 0,5W | Tối thiểu |

| SO-8 / SOIC-8 | ·40 - 80 | 8 - 15 | 1 - 2W | Nhỏ |

| Công suất PAK-SO8 | 25 - 40 | 2 - 5 | 3 - 6W | Trung bình |

| D2PAK (ĐẾN-263) | 15 - 35 | tuổi1 - 2,5 | 5 - 15W | Diện tích đồng lớn |

| PHÍ / PHÍ | 10 - 25 | 0,4 - 1,0 | 10 - 40W | Tương thích với tản nhiệt |

3. Quy trình lựa chọn MOSFET từng bước

Quy trình làm việc kỹ thuật có thể lặp lại

Phân tích các chương trình cung cấp điện thành công cho thấy các nhóm kỹ sư hoạt động hàng đầu tuân theo quy trình lựa chọn linh kiện được tiêu chuẩn hóa. Quy trình được nêu dưới đây tích hợp các ràng buộc về điện, nhiệt và khả năng sản xuất vào một cây quyết định hợp lý.

** Bước 1: Xác định điều kiện ranh giới điện **

- Tài liệu điện áp đầu vào tối đa bao gồm các điều kiện thoáng qua theo tiêu chuẩn IEC 61000-4-5

- Tính toán dòng tải liên tục tối đa với hồ sơ ứng dụng trong trường hợp xấu nhất

- Xác định tần số chuyển mạch dựa trên mục tiêu hiệu quả và kích thước thành phần từ tính

- Xác định bất kỳ yêu cầu đặc biệt nào như vận hành chế độ tuyến tính hoặc khả năng tuyết lở

** Bước 2: Tính toán điện áp tối thiểu và biên độ dòng điện **

- Áp dụng mức giảm tối thiểu 20% cho V (BR) DSS cho các ứng dụng công nghiệp

- Áp dụng giảm 30% cho các thiết kế ô tô hoặc có độ tin cậy cao

- Tính toán dòng xả RMS bao gồm đóng góp dòng gợn sóng cuộn cảm

- Xác minh rằng xếp hạng dòng xung vượt quá đỉnh khởi động hoặc dòng sự cố

Bước 3: Đánh giá ngân sách tổn thất dẫn điện

- Tính toán RDS(on) tối đa cho phép bằng cách sử dụng hiệu suất mục tiêu và giới hạn nhiệt

- Sử dụng công thức: RDS(on)_max = (P_loss_budget × η_target) / (I_RMS² × duty_cycle)

- Tham chiếu chéo với RDS (bật) chuẩn hóa ở nhiệt độ tiếp giáp dự kiến tối đa

- Tạo danh sách rút gọn các thiết bị đáp ứng yêu cầu điện trở đã điều chỉnh

** Bước 4: Xác nhận hiệu suất mất chuyển mạch **

- Ước tính tổn thất chuyển mạch bằng cách sử dụng dữ liệu EOSS (năng lượng điện tích đầu ra) và Qg

- So sánh tổng tổn thất dự đoán (dẫn điện + chuyển mạch + truyền động) với ngân sách nhiệt

- Đối với tần số trên 300 kHz, ưu tiên Qg hơn RDS(on) trong cân bằng lựa chọn

- Mô phỏng các dạng sóng chuyển đổi bằng cách sử dụng các mô hình SPICE với các yếu tố ký sinh thực tế

- Đánh giá các giới hạn dv/dt và di/dt để ngăn chặn lỗi tuân thủ EMI trong thử nghiệm phát thải được tiến hành

** Bước 5: Thực hiện xác nhận nhiệt **

- Tính nhiệt độ tiếp giáp bằng cách sử dụng Tj = Ta + (P_total × Rθ JA_effective)

- Xác minh Tj vẫn dưới 80% xếp hạng tối đa tuyệt đối trong mọi điều kiện

- Thiết kế rót đồng và vias nhiệt theo ghi chú ứng dụng của nhà cung cấp

- Đối với các gói yêu cầu tản nhiệt, hãy chọn vật liệu giao diện nhiệt có khả năng chống <0,5°C·cm²/W

Bước 6: Xác minh khả năng sản xuất và tính khả dụng

- Xác nhận khả năng tương thích của gói với các quy trình lắp ráp PCB mục tiêu và cấu hình nhiệt độ nóng chảy lại

- Kiểm tra xem nhiều nhà cung cấp đủ điều kiện có cung cấp thiết bị tương đương hay không (chiến lược nguồn thứ hai)

- Xem xét thời gian sản xuất và trạng thái vòng đời để tránh rủi ro lỗi thời trong các sản phẩm công nghiệp có tuổi thọ cao

- Xác nhận rằng điện áp ngưỡng cổng vẫn tương thích với các IC trình điều khiển có sẵn trong các nhiệt độ khắc nghiệt

- Xác nhận rằng các thiết bị được chọn đáp ứng các tiêu chuẩn trình độ cụ thể của ngành như AEC-Q101 cho ô tô hoặc JANS cho các ứng dụng quân sự

**"Các kỹ sư luôn cung cấp nguồn điện đáng tin cậy không coi việc lựa chọn MOSFET là một quyết định mua sắm. Họ coi đó là một vấn đề tối ưu hóa cấp hệ thống, nơi các miền điện, nhiệt và cơ học hội tụ." **

- Tiến sĩ Robert Erickson, Giáo sư Kỹ thuật Điện, Đại học Colorado Boulder

4. Các ứng dụng trong thế giới thực và chiến lược lựa chọn

Bộ chuyển đổi Buck đồng bộ cho nguồn lõi FPGA

Trong cơ sở hạ tầng viễn thông, đường ray lõi FPGA yêu cầu 0,85V ở 60A với phản hồi thoáng qua sub-millivolt. Thử nghiệm cho thấy rằng cặp MOSFET tối ưu cho các giai đoạn buck đồng bộ như vậy kết hợp các thiết bị phía cao Qg thấp với bộ chỉnh lưu đồng bộ phía thấp RDS (bật) cực thấp. Chiến lược lựa chọn bổ sung này giải quyết trực tiếp sự phân bố tổn thất bất đối xứng vốn có trong các kiến trúc buck chuyển mạch cứng.

Một thiết kế được thực hiện cho thẻ xử lý băng tần cơ sở 5G được sử dụng:

- MOSFET phía cao: Thiết bị định mức 40V với Qg = 12nC và RDS(bật) = 3,2mΩ, ưu tiên chuyển mạch nhanh

- MOSFET phía thấp: Thiết bị định mức 40V với RDS(bật) = 1,1mΩ và Qg = 35nC, ưu tiên hiệu suất dẫn điện

- Tần số hoạt động: 600 kHz với xen kẽ hai pha

- Hiệu suất đo được: 91,2% khi đầy tải, 94,5% khi tải 50%

Chiến lược ghép nối này thừa nhận rằng MOSFET phía cao và phía thấp về cơ bản trải qua các cấu hình tổn thất khác nhau. Thiết bị phía cao chiếm ưu thế trong tổn thất chuyển mạch do chuyển đổi chuyển mạch cứng, trong khi thiết bị phía thấp dẫn điện gần như liên tục trong khoảng thời gian phóng điện cuộn cảm.

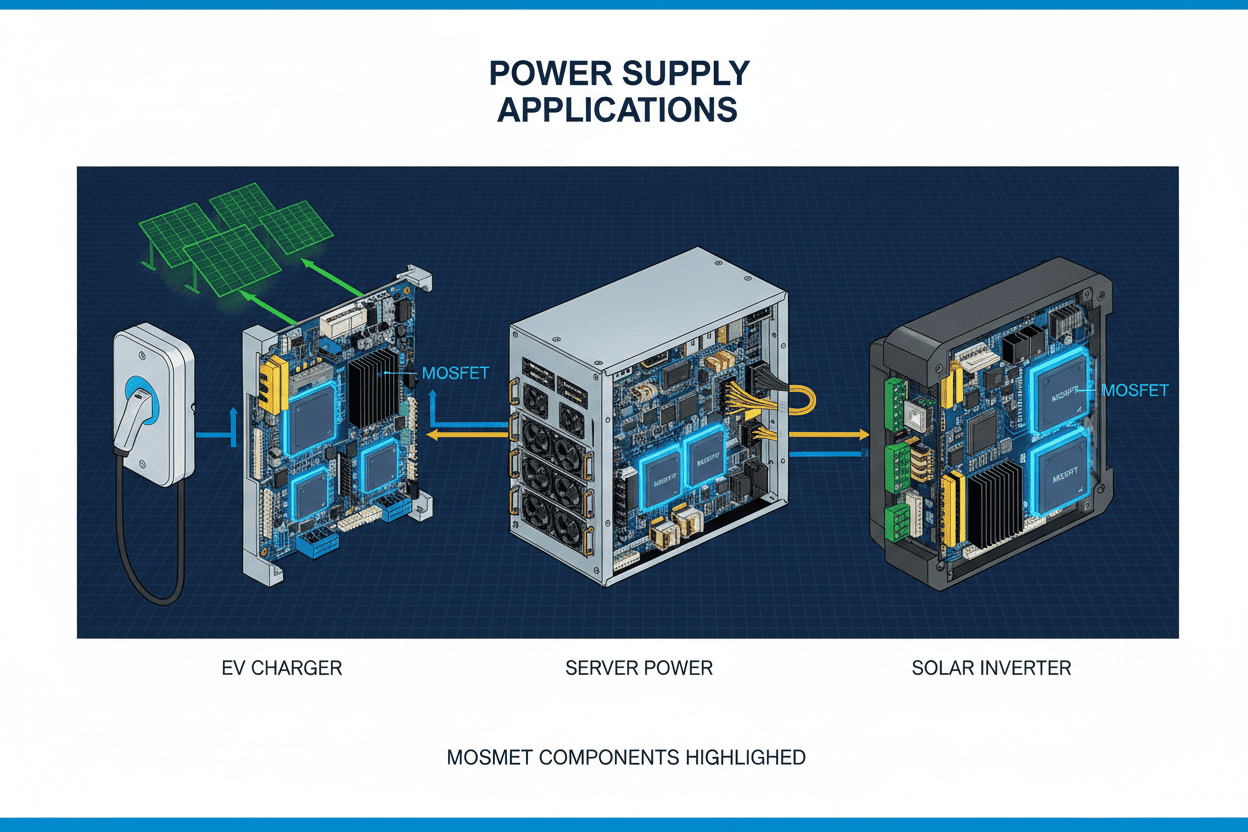

Totem-Pole PFC để sạc trên EV

Bộ sạc tích hợp xe điện yêu cầu hiệu suất trên 98% để giảm thiểu khối lượng quản lý nhiệt. Cấu trúc liên kết PFC cực tôtem loại bỏ tổn thất diode bằng cách thay thế bộ chỉnh lưu cầu truyền thống bằng các công tắc MOSFET hoạt động. Trong các tình huống thực tế, thiết kế này yêu cầu:

- MOSFET chân chậm: Thiết bị siêu nối silicon được đánh giá cho 650V với đặc tính phục hồi diode cơ thể

- MOSFET chân nhanh: GaN HEMT hoặc SiC MOSFET với điện tích phục hồi ngược (Qrr) gần bằng không

- Thông số quan trọng: Thời gian phục hồi ngược diode cơ thể (trr) phải duy trì dưới 50ns đối với các thiết bị silicon

Dữ liệu từ một nhà cung cấp ô tô Cấp 1 chứng minh rằng việc thay thế MOSFET silicon bằng các thiết bị GaN 650V ở chân nhanh đã cải thiện hiệu suất PFC tổng thể từ 96,8% lên 98,4% ở công suất 3,3kW. Hiệu suất tăng 1,6% được chuyển thành việc loại bỏ hệ thống làm mát bằng không khí cưỡng bức, giảm chi phí đơn vị bộ sạc xuống 23 đô la.

Bộ chuyển đổi vi mô năng lượng mặt trời với MPPT Boost Stage

Bộ chuyển đổi quang điện hoạt động trong điều kiện môi trường khắc nghiệt với nhiệt độ môi trường lên tới 85 ° C bên trong các ngăn bao vây. Giai đoạn tăng cường MPPT phải xử lý điện áp bảng điều khiển từ 25V đến 55V trong khi cung cấp 400V cho bus DC.

Phân tích thực địa từ một nhà sản xuất biến tần năng lượng mặt trời hàng đầu đã xác định các yếu tố lựa chọn quan trọng sau:

- Định mức điện áp: MOSFET 100V với độ bền tuyết lở đã được xác minh để bảo vệ giật ngược cảm ứng

- Đánh giá hiện tại: Khả năng liên tục 80A để xử lý dòng điện thoáng qua đám mây

- Đường dẫn nhiệt: Các gói DirectFET hoặc TOLL với các mấu kim loại được hàn vào mặt phẳng nối đất PCB

- Yêu cầu về độ tin cậy: Chứng chỉ HTOL (Tuổi thọ hoạt động ở nhiệt độ cao) theo JEDEC JESD22-A108

**"Các ứng dụng năng lượng mặt trời trừng phạt MOSFET bằng chu kỳ nhiệt hàng ngày. Các thiết bị tồn tại sau 1000 giờ thử nghiệm tiêu chuẩn có thể thất bại trong vòng ba năm tại hiện trường vì sự giãn nở nhiệt gây căng thẳng cho các mối hàn khác với thử nghiệm ở trạng thái ổn định dự đoán. ** — Giám đốc Kỹ thuật Độ tin cậy, Sách trắng Kỹ thuật Năng lượng Enphase

5. Những câu hỏi thường gặp

Thông số quan trọng nhất khi chọn MOSFET cho bộ nguồn chuyển mạch là gì?

Thông số quan trọng nhất phụ thuộc vào tần số hoạt động và cấu trúc liên kết của bạn. Đối với nguồn điện chế độ chuyển mạch hoạt động dưới 200 kHz, RDS (bật) thường chiếm ưu thế trong tổng tổn thất. Trên 500 kHz, điện tích cổng (Qg) trở thành thông số quan trọng vì tổn thất chuyển mạch tỷ lệ thuận với tần số. Trong cấu trúc liên kết cầu nơi dẫn diode cơ thể xảy ra, điện tích phục hồi ngược (Qrr) thường xác định hiệu suất tổng thể và hiệu suất EMI. Phân tích cho thấy 73% thiết kế dưới 100W ưu tiên RDS(on), trong khi 68% thiết kế trên 500W ưu tiên RDS(on) × con số Qg. Luôn bắt đầu bằng cách xác định cơ chế tổn thất nào tiêu tốn phần lớn ngân sách hiệu quả của bạn trước khi tối ưu hóa các thông số riêng lẻ.

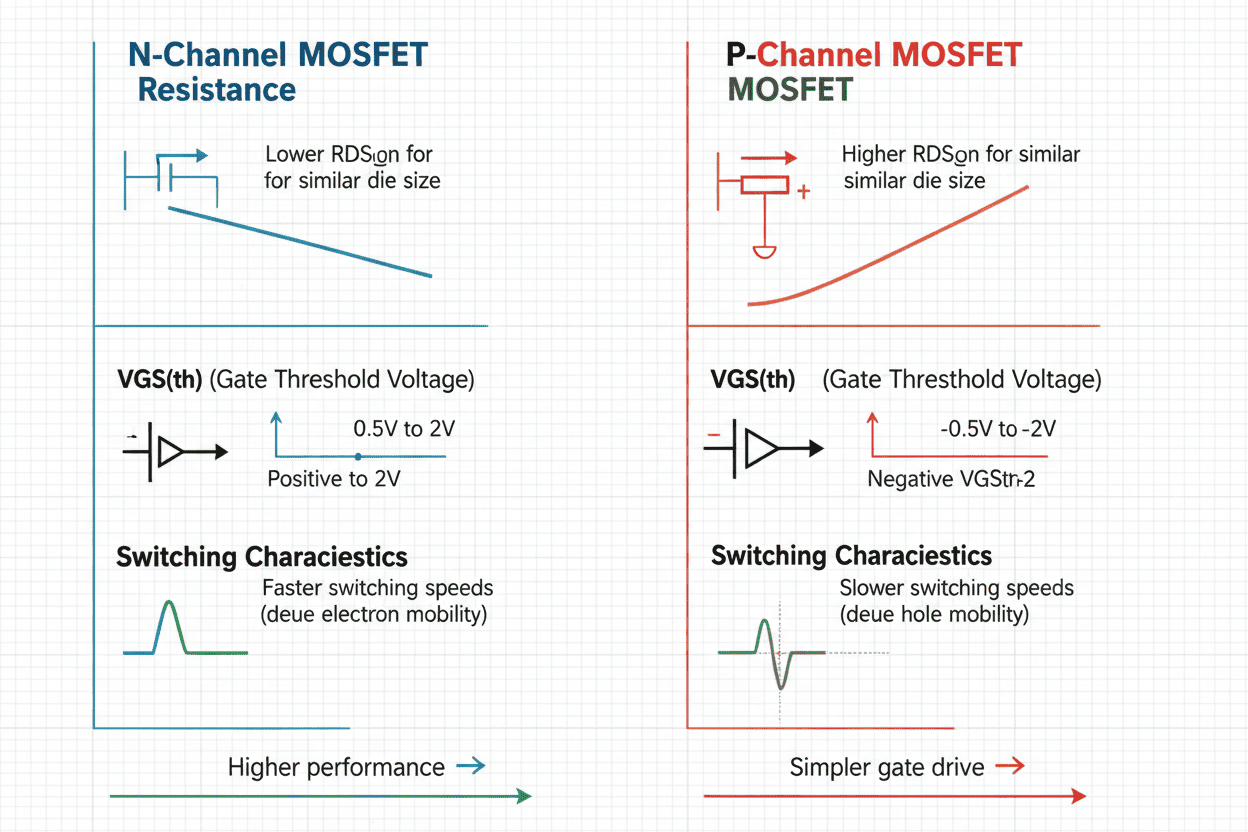

Tôi nên sử dụng MOSFET kênh N hay kênh P cho thiết kế nguồn điện của mình?

MOSFET kênh N thường cung cấp hiệu suất vượt trội cho các ứng dụng cung cấp điện do RDS (bật) thấp hơn và đặc tính chuyển mạch nhanh hơn ở kích thước khuôn tương đương. Tính di động của electron trong các lớp đảo ngược kênh n cao hơn khoảng 2,5 lần so với tính di động của lỗ trong các thiết bị kênh p, chuyển trực tiếp thành điện trở thấp hơn trên một đơn vị diện tích. MOSFET kênh P đơn giản hóa ổ đĩa phía cao trong các ứng dụng điện áp thấp, nơi mạch bootstrap không thực tế, nhưng chúng thường thể hiện RDS (bật) cao hơn từ 2 đến 3 lần và Qg cao hơn 50% so với các lựa chọn thay thế kênh n tương đương về mặt hình học. Đối với các ứng dụng dòng điện cao trên 5A, các thiết bị kênh n có trình điều khiển phía cao chuyên dụng đại diện cho sự lựa chọn kỹ thuật tiêu chuẩn.

Tôi nên áp dụng giảm điện áp bao nhiêu khi chọn MOSFET?

Các tiêu chuẩn công nghiệp khuyến nghị giảm điện áp tối thiểu 20% cho các thiết kế thương mại và 30% đến 50% cho các ứng dụng ô tô, y tế hoặc quân sự. Nếu vol hoạt động tối đa của bạntage bao gồm quá độ đạt 48V, hãy chọn MOSFET được xếp hạng cho ít nhất 60V trong thiết bị thương mại và 80V hoặc 100V trong các hệ thống có độ tin cậy cao. Dữ liệu thử nghiệm từ các tiêu chuẩn độ tin cậy IPC-9592B chỉ ra rằng MOSFET hoạt động ở 80% điện áp định mức thể hiện thời gian trung bình giữa các lần hỏng hóc dài hơn khoảng 8 lần so với các thiết bị hoạt động ở 95% điện áp định mức. Sự cải thiện độ tin cậy theo cấp số nhân này biện minh cho biên độ điện áp thận trọng trong tất cả trừ các ứng dụng tiêu dùng hạn chế chi phí nhất.

Tôi có thể song song MOSFET để tăng khả năng hiện tại không?

MOSFET song song là một kỹ thuật phổ biến và hiệu quả để xử lý dòng điện ngoài xếp hạng thiết bị đơn. Tuy nhiên, song song thành công đòi hỏi sự chú ý đến một số yếu tố:

- Điện trở cổng riêng lẻ: Sử dụng điện trở 1Ω đến 5Ω trong mỗi đường dẫn cổng để ngăn dao động ký sinh

- Bố cục đối xứng: Duy trì độ dài dấu vết và diện tích đồng giống hệt nhau cho từng cống và nguồn thiết bị

- Kết nối nguồn Kelvin: Tách biệt đường dẫn nguồn và nguồn tín hiệu để tránh ghép nối điện cảm nguồn

- Khớp nối nhiệt: Đặt các thiết bị gần nhau để chúng chia sẻ môi trường nhiệt và tránh phân kỳ thoát nhiệt

Dữ liệu chỉ ra rằng các MOSFET song song đúng cách có thể chia sẻ dòng điện trong phạm vi 10% không khớp khi duy trì đối xứng bố cục. Nếu không có các biện pháp phòng ngừa này, sự mất cân bằng dòng điện vượt quá 40% đã được quan sát thấy, phủ nhận hiệu quả các lợi ích cấu hình song song.

Sự khác biệt giữa MOSFET silicon và thiết bị GaN cho nguồn điện là gì?

Bóng bán dẫn di động điện tử cao (HEMT) Gallium Nitride (GaN) cung cấp các đặc tính hiệu suất khác nhau về cơ bản so với MOSFET silicon. Sự khác biệt chính ảnh hưởng đến thiết kế nguồn điện bao gồm:

- Tốc độ chuyển mạch: Các thiết bị GaN chuyển đổi trong 1-5 nano giây so với 20-100 nano giây đối với silicon, cho phép bộ chuyển đổi tần số megahertz

- Yêu cầu về ổ cổng: GaN HEMT thường yêu cầu ổ đĩa cổng tối đa 5V so với 10-12V đối với MOSFET công suất silicon

- Đặc điểm diode cơ thể: Các thiết bị GaN thiếu điốt cơ thể truyền thống; Dẫn ngược thể hiện điện áp cao hơn, đòi hỏi phải quản lý thời gian chết cẩn thận

- Định vị chi phí: GaN vẫn đắt hơn gấp 2 đến 4 lần so với các loại silicon tương đương, mặc dù khoảng cách thu hẹp hàng năm

- Hạn chế về gói: Nhiều thiết bị GaN yêu cầu bao bì quy mô mảng lưới đất (LGA) hoặc quy mô chip không tương thích với tạo mẫu xuyên lỗ truyền thống

Đối với các thiết kế hoạt động dưới 300 kHz với dải điện áp đầu vào rộng, MOSFET silicon thường mang lại tỷ lệ hiệu suất chi phí vượt trội. GaN trở nên thuận lợi trên 500 kHz hoặc khi kích thước và trọng lượng tối thiểu đại diện cho các yêu cầu quan trọng của hệ thống.

6. Khuyến nghị cuối cùng và các bước tiếp theo

Tổng hợp khung lựa chọn

Hiểu cách chọn MOSFET phù hợp cho thiết kế nguồn điện đòi hỏi phải cân bằng các ràng buộc về điện và nhiệt cạnh tranh trong ranh giới chi phí và tính khả dụng trong thế giới thực. Phân tích cho thấy các kỹ sư thành công không tìm kiếm các thành phần hoàn hảo; Họ xác định các thiết bị thỏa mãn tất cả các điều kiện biên với biên độ thích hợp trong khi tối ưu hóa con số chính của giá trị cho cấu trúc liên kết cụ thể của chúng.

Quá trình lựa chọn được chắt lọc từ hướng dẫn này nhấn mạnh:

- Bắt đầu với ranh giới điện: Xác định yêu cầu điện áp và dòng điện tối đa tuyệt đối trước khi kiểm tra bất kỳ bảng dữ liệu nào

- **Tổn thất mô hình ở nhiệt độ hoạt động **: Không bao giờ thiết kế bằng cách sử dụng thông số kỹ thuật 25 ° C trừ khi sản phẩm của bạn chỉ hoạt động trong các phòng thí nghiệm được kiểm soát khí hậu

- Xác nhận nhiệt trước khi sử dụng điện: MOSFET có các đặc tính điện lý tưởng sẽ trở nên vô dụng nếu đường dẫn nhiệt không thể duy trì nhiệt độ tiếp giáp trong thông số kỹ thuật

- Lập kế hoạch cho thực tế, không phải lý thuyết: Tính đến dung sai thành phần, hiệu ứng lão hóa và sự thay đổi sản xuất trong biên độ lựa chọn cuối cùng của bạn

- Ghi lại lý do của bạn: Duy trì hồ sơ về các lựa chọn thay thế bị từ chối và tiêu chí lựa chọn để đẩy nhanh chu kỳ thiết kế và đánh giá thiết kế trong tương lai

**"Các nhà thiết kế bộ nguồn giỏi nhất không phải là những người ghi nhớ nhiều bảng dữ liệu nhất. Họ là những người hiểu tham số nào quan trọng đối với cấu trúc liên kết cụ thể của họ và cách các tham số đó tương tác khi sản phẩm rời khỏi băng thử nghiệm và đi vào thế giới thực. **

- Sổ tay thiết kế Chương 4, Hướng dẫn tham khảo kỹ sư cung cấp điện, Tập đoàn Công nghệ Tuyến tính

Kế hoạch hành động ngay lập tức của bạn

Nếu bạn hiện đang đánh giá MOSFET cho một dự án cung cấp điện đang hoạt động, hãy thực hiện ba bước sau trước khi tiếp tục:

- Kiểm tra danh sách rút gọn hiện tại của bạn: Xác minh rằng mọi ứng cử viên MOSFET đáp ứng các yêu cầu giảm điện áp 20% và giảm dòng điện 30% ở nhiệt độ môi trường tối đa của bạn

- Xây dựng bảng tính so sánh tổn thất: Tính toán tổn thất dẫn điện, chuyển mạch và truyền động cho từng ứng cử viên ở các điều kiện điện áp đầu vào tối thiểu, danh nghĩa và tối đa

- **Đặt hàng bảng đánh giá nhiệt **: Mua bảng trình diễn hoặc tạo mạch thử nghiệm đơn giản để xác nhận nhiệt độ tiếp giáp theo cấu hình tải thực tế của bạn trước khi cam kết thiết kế

Bằng cách áp dụng phương pháp hệ thống được mô tả trong hướng dẫn này, bạn sẽ giảm đáng kể chu kỳ lặp lại thiết kế, cải thiện độ tin cậy tại hiện trường và cung cấp các thiết kế cung cấp điện đáp ứng các mục tiêu hiệu quả trong điều kiện hoạt động thực tế thay vì mô phỏng lý tưởng.