Quang học đồng đóng gói (CPO) trong trung tâm dữ liệu AI: Kiến trúc, sự đánh đổi và thực tế kỹ thuật

Quang học đồng đóng gói (CPO) tích hợp động cơ quang học trực tiếp với ASIC chuyển mạch ở cấp độ gói, rút ngắn đáng kể các kết nối điện. Điều này làm giảm mức tiêu thụ điện năng của SerDes, cải thiện mật độ băng thông và tăng cường tính toàn vẹn của tín hiệu. CPO đang nổi lên như một yếu tố hỗ trợ chính cho 800G, 1.6T và hơn thế nữa, đặc biệt là trong các mạng trung tâm dữ liệu do AI điều khiển. Tuy nhiên, nó đặt ra những thách thức kỹ thuật mới trong quản lý nhiệt, độ tin cậy, khả năng sản xuất và khả năng bảo dưỡng. Bài viết này cung cấp phân tích kỹ thuật chuyên sâu về kiến trúc CPO, các thành phần hệ thống, hạn chế nhiệt, sự đánh đổi vận hành và tác động của nó so với quang học có thể cắm truyền thống.

Mục lục

- 1. Các nguyên tắc cơ bản về kỹ thuật của CPO

- 2. Tại sao các trung tâm dữ liệu AI đang thúc đẩy việc áp dụng CPO

- [3. Kiến trúc hệ thống CPO và các thành phần chính] (# 3-cpo-system-architecture-and-key-components)

- [4. Đường dẫn tín hiệu và cơ chế hoạt động] (# 4-đường dẫn tín hiệu và cơ chế hoạt động)

- [5. Thách thức về thiết kế nhiệt và độ tin cậy] (#5-thách thức về thiết kế nhiệt và độ tin cậy)

- [6. Lợi ích hiệu suất và giá trị hệ thống] (# 6-hiệu suất-lợi ích-và-giá trị hệ thống)

- 7. Tác động đến bảo trì trung tâm dữ liệu

- 8. Các vấn đề thường gặp và giải pháp kỹ thuật

- [9. CPO vs Quang học có thể cắm được] (# 9-cpo-vs-pluggable-optics)

- [10. Lộ trình tốc độ và sự phát triển công nghệ] (# 10-lộ trình tốc độ và tiến hóa công nghệ)

- [11. Câu hỏi thường gặp](#11-câu hỏi thường gặp)

1. Các nguyên tắc cơ bản về kỹ thuật của CPO

Quang học đồng đóng gói (CPO) về cơ bản là một ** cách tiếp cận đồng thiết kế giữa quang tử và bao bì bán dẫn tiên tiến **. Thay vì định tuyến tín hiệu điện tốc độ cao qua các dấu vết PCB dài đến các mô-đun quang ở bảng điều khiển phía trước, CPO đặt động cơ quang gần ASIC của công tắc trong cùng một gói hoặc chất nền.

Sự thay đổi kiến trúc này dẫn đến:

- Giảm chiều dài dấu vết điện từ cm xuống milimét

- Giảm đáng kể mức tiêu thụ điện năng của SerDes (thường là 20–40%)

- Cải thiện tính toàn vẹn của tín hiệu (giảm mất chèn và chập chờn)

- Giảm sự phụ thuộc vào vật liệu PCB cao cấp và bộ hẹn giờ

CPO về cơ bản xác định lại ranh giới giữa miền điện và quang trong mạng trung tâm dữ liệu.

2. Tại sao các trung tâm dữ liệu AI đang thúc đẩy việc áp dụng CPO

Khối lượng công việc AI, đặc biệt là đào tạo phân tán, đặt ra yêu cầu cực kỳ cao đối với cơ sở hạ tầng mạng:

- Băng thông cực cao (kết nối cấp Tbps)

- Độ trễ thấp (giao tiếp quy mô micro giây)

- Hiệu suất năng lượng cao (tối ưu hóa W / Gbps)

Quang học có thể cắm truyền thống phải đối mặt với một số hạn chế:

- Tăng mức tiêu thụ điện năng SerDes ở 112G / 224G PAM4

- Suy giảm tín hiệu trên các dấu vết PCB dài

- Giới hạn mật độ băng thông ở bảng điều khiển phía trước

CPO giải quyết những hạn chế này bằng cách di chuyển quang học đến gần hơn với điện toán, cho phép:

- Giảm tổn thất điện

- Đường dẫn dữ liệu có độ trễ thấp hơn

- Mật độ cổng và khả năng mở rộng cao hơn

Điều này làm cho CPO đặc biệt phù hợp với các cụm GPU quy mô lớn và kết cấu đào tạo AI.

3. Kiến trúc hệ thống CPO và các thành phần chính

3.1 Các thành phần cốt lõi

** 1) Chuyển đổi ASIC **

- Cung cấp khả năng chuyển mạch cấp Tbps

- Tích hợp SerDes tốc độ cao (112G / 224G PAM4)

** 2) Động cơ quang học **

- Thực hiện chuyển đổi điện sang quang (E/O) và quang thành điện (O/E)

- Thường dựa trên quang tử silicon (SiPh) hoặc indium phosphide (InP)

** 3) Nguồn laser **

- Thường được triển khai dưới dạng Nguồn Laser bên ngoài (ELS)

- Cải thiện độ ổn định nhiệt và độ tin cậy

** 4) Chất nền gói / Interposer **

- Cho phép kết nối mật độ cao

- Hỗ trợ đóng gói nâng cao (tích hợp 2.5D / 3D)

** 5) Giao diện khớp nối sợi quang **

- Sử dụng cách tử hoặc khớp nối cạnh

- Yêu cầu độ chính xác căn chỉnh cấp micron

4. Đường dẫn tín hiệu và cơ chế hoạt động

Luồng tín hiệu CPO có thể được mô tả như sau:

- Công tắc ASIC tạo ra tín hiệu điện tốc độ cao

- Tín hiệu truyền qua các kết nối điện cực ngắn (<10 mm)

- Động cơ quang chuyển đổi tín hiệu điện thành tín hiệu quang

- Tín hiệu quang được truyền qua sợi quang với tổn thất tối thiểu

- Tại máy thu, tín hiệu quang được chuyển đổi trở lại thành tín hiệu điện

Tối ưu hóa kỹ thuật chính:

- Loại bỏ bộ hẹn giờ

- Giảm chi phí sửa lỗi chuyển tiếp (FEC)

- Tỷ lệ lỗi bit thấp hơn (BER)

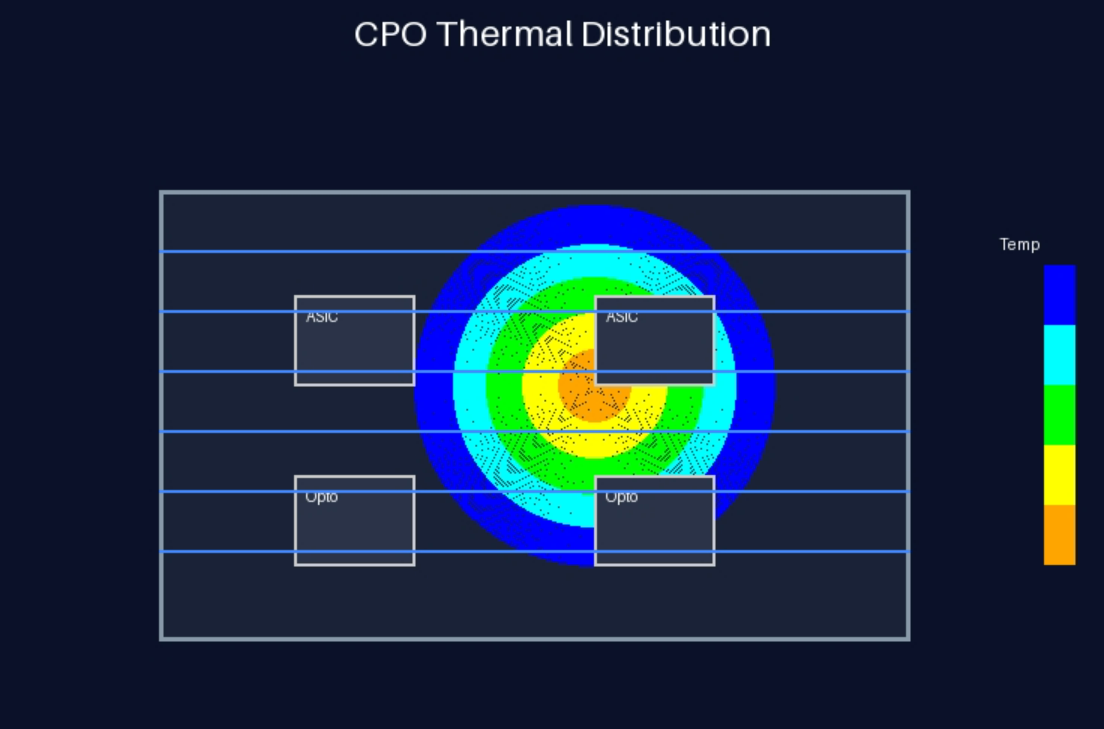

5. Thách thức về thiết kế nhiệt và độ tin cậy

5.1 Các vấn đề về khớp nối nhiệt

CPO đưa ra một thách thức quan trọng: đặt ASIC công suất cao cùng với các thành phần quang học nhạy cảm với nhiệt.

- Công suất ASIC: thường là 400W–800W+

- Các thành phần quang học yêu cầu nhiệt độ ổn định và tương đối thấp hơn

Điều này tạo ra các yêu cầu nhiệt mâu thuẫn trong một diện tích nhỏ gọn.

5.2 Giải pháp kỹ thuật

- Cấu trúc cách ly nhiệt giữa ASIC và quang học

- Hệ thống làm mát bằng chất lỏng trực tiếp đến chip

- Kiến trúc Nguồn Laser Bên ngoài (ELS)

- Bộ làm mát nhiệt điện (TEC) để điều khiển chính xác

5.3 Rủi ro độ tin cậy dài hạn

- Chu kỳ nhiệt dẫn đến ứng suất cơ học

- Suy thoái bằng laser theo thời gian

- Độ lệch căn chỉnh quang học ảnh hưởng đến hiệu quả khớp nối

6. Lợi ích hiệu suất và giá trị hệ thống

Giá trị của CPO không chỉ nằm ở tốc độ cao hơn mà còn ở việc cho phép tốc độ cao hơn một cách hiệu quả:

- Giảm năng lượng: ~20–40%

- Mật độ băng thông: >2× cải thiện

- Giảm độ trễ thông qua các đường dẫn điện ngắn hơn

- Khả năng mở rộng nâng cao cho các cụm AI lớn

Những lợi thế này ảnh hưởng trực tiếp đến hiệu quả đào tạo phân tán và hiệu suất cấp hệ thống.

7. Tác động đến bảo trì trung tâm dữ liệu

CPO thay đổi đáng kể quy trình bảo trì truyền thống:

| Khía cạnh | Quang học có thể cắm | đượcCPO |

|---|---|---|

| ly thất bại | Cấp mô-đun | Cấpbảng/hệ thống |

| pháp thay thế | Có thể thay thế nóng | Thay thế toàn bộ bảng |

| MTTR | Thấp | Cao |

| phức tạp trong hoạt động | Thấp | Cao |

Ý nghĩa hoạt động:

- Tăng nhu cầu bảo trì dự đoán

- Hệ thống giám sát và đo từ xa nâng cao

- Phụ thuộc nhiều hơn vào dự phòng (ví dụ: kiến trúc N+1)

8. Các vấn đề thường gặp và giải pháp kỹ thuật

| đề | Nguyên nhân gốc rễ | Giải pháp |

|---|---|---|

| Nhiễu nhiệt | Khớp nối nhiệt quang học ASIC | Cách ly nhiệt + làm mát bằng chất lỏng |

| Khả năng phục vụ kém | Mức độ tích hợp cao | Thiết kế CPO mô-đun |

| Độ phức tạp trong sản xuất | Căn chỉnh quang học có độ chính xác cao | Quy trình đóng gói tự động |

| Biến đổi suy hao quang học | Trôi nhiệt độ | Điều khiển dựa trên TEC |

| Chi phí cao | Chế tạo phức tạp | Tiêu chuẩn hóa và mở rộng quy mô |

9. CPO so với quang học có thể cắm được

| Kích thước | CPO | Quang học có thể cắm | được

|---|---|---|

| Kiến trúc | Tích hợp cấp gói | Mô-đun bảng điều khiển phía trước |

| Hiệu quả năng lượng | Tiêu thụ điện năng thấp | Tiêu thụ điện năng cao hơn |

| Băng thông | Cực cao | Giới hạn ở tốc độ cực cao |

| Khả năng phục vụ | Khó khăn | Dễ dàng |

| Quản lý nhiệt | Phức tạp | Đơn giản hơn |

| Đáo hạn | Mới nổi | Trưởng thành |

Kết luận:

CPO và quang học có thể cắm được sẽ cùng tồn tại trong ngắn hạn và trung hạn. CPO chủ yếu sẽ được triển khai trong các cụm AI siêu quy mô yêu cầu mật độ băng thông cực cao.

10. Lộ trình tốc độ và sự phát triển của công nghệ

Mục tiêu tốc độ hiện tại và tương lai:

- 800G (hiện đang triển khai)

- 1.6T (đang phát triển)

- 3.2T (lộ trình tương lai)

Các công nghệ hỗ trợ chính:

- 224G SerDes

- Quang tử silicon (SiPh)

- Bao bì tiên tiến (tích hợp 2.5D / 3D)

- Kiến trúc laser bên ngoài

CPO được định vị là một giải pháp lâu dài để khắc phục các giới hạn mở rộng quy mô I/O điện.

11. Câu hỏi thường gặp

Q1: CPO sẽ thay thế hoàn toàn quang học có thể cắm được?

Không. Cả hai công nghệ sẽ cùng tồn tại. CPO phù hợp nhất cho môi trường AI băng thông cực cao, trong khi quang học có thể cắm được vẫn thiết thực cho mạng mục đích chung.

Q2: Thách thức lớn nhất trong việc triển khai CPO là gì?

Quản lý nhiệt và khả năng sử dụng là những nút thắt kỹ thuật chính.

Q3: Tại sao kiến trúc laser bên ngoài được ưa chuộng hơn?

Nó làm giảm tải nhiệt trong gói và cải thiện tuổi thọ laser và độ tin cậy của hệ thống.

Q4: Lợi ích thực sự của CPO trong khối lượng công việc AI là gì?

Nó làm giảm mức tiêu thụ điện năng truyền thông và tăng mật độ băng thông, cải thiện hiệu quả đào tạo tổng thể và khả năng mở rộng.